Modul 3 Counter

Modul 3

Counter

1. Tujuan [Kembali]

- Merangkai dan Menguji operasi logika dari counter asyncron dan counter syncronous.

- Merangkai dan Menguji aplikasi dari sebuah Counter.

2. Alat dan Bahan [Kembali]

3. Dasar Teori [Kembali]

3.3 Counter

Counter adalah sebuah rangkaian sekuensial yang mengeluarkan urutan statestate tertentu, yang merupakan aplikasi dari pulsa-pulsa inputnya. Pulsa input dapat berupa pulsa clock atau pulsa yang dibangkitkan oleh sumber eksternal dan muncul pada interval waktu tertentu. Counter banyak digunakan pada peralatan yang berhubungan dengan teknologi digital, biasanya untuk menghitung jumlah kemunculan sebuah o kejadian/event atau untuk menghitung pembangkit waktu. Counter yang mengeluarkan urutan biner dinamakan Biner Counter. Sebuah n-bit binary counter terdiri dari n buah flip- flop, dapat menghitung dari 0 sampai 2n - 1 . Counter secara umum diklasifikasikan atas counter asyncron dan counter syncronous.

a. Counter Asyncronous

Counter Asyncronous disebut juga Ripple Through Counter atau Counter

Serial (Serial Counter), karena output masing-masing flip-flop yang digunakan

akan bergulingan (berubah kondisi dan “0” ke “1”) dan sebaliknya secara

berurutan atau langkah demi langkah, hal ini disebabkan karena hanya flipflop

yang paling ujung saja yang dikendalikan oleh sinyal clock, sedangkan sinyal

clock untuk flip-flop lainnya diambilkan dan masing-masing flip-flop

sebelumnya.

|

| Gambar 3.3 Rangkaian Counter Asycronous |

b. Counter Syncronous

Counter syncronous disebut sebagai Counter parallel, output flipflop yang

digunakan bergulingan secara serempak. Hal ini disebabkan karena masing-

masing flip- flop tersebut dikendalikan secara serempak oleh sinyal clock.

|

| Gambar 3.4 Rangkaian Counter Syncronous |

4. Percobaan [Kembali]

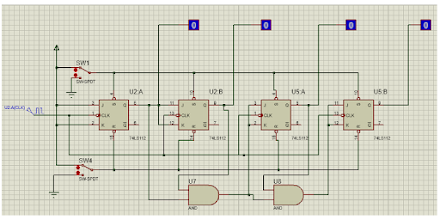

3.4.1 Percobaan 1 Asyncronous Binary Counter 4 bit degan 4 J-K flip-flop.

1. Rangkai rangkaian seperti gambar dibawah ini.

|

| Gambar 3.5 Rangkaian percobaan Asynchronous Binary Counter 4 bit |

|

| Gambar 3.6 Rangkaian percobaan Asynchronous Binary Counter 4 bit |

3.4.2 Percobaan 2 Asyncronous Binary Counter

1. Rangkai rangkaian seperti gambar dibawah ini.

|

| Gambar 3.7 Rangkaian Asynchronous Binary Counter |

|

| Gambar 3.8 Rangkaian Asynchronous Binary Counter Percobaan 2a |

3. Cek dan catat output yang terjadi melalui LED ke jurnal

4. Matikan power supply, lepaskan jumper CLK2 yang terhubung ke sumber clock, kemudian hubungkan QA dengan CLK2 pada masing masing counter dan ulangi langkah 2 dan 3

|

| Gambar 3.9 Rangkaian Asynchronous Binary Counter Percobaan 2b |

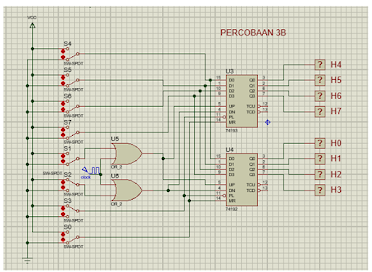

3.4.3 Percobaan 3 Synchoronous Binary Counter

|

| Gambar 3.10 Rangkaian percobaan Synchronous binary counter |

|

| Gambar 3.11 Rangkaian percobaan Synchronous binary counter |

|

| Gambar 3.12 Rangkaian Synchronous binary counter percobaan 3b |

Komentar

Posting Komentar