Laporan Akhir 1

1. Jurnal [kembali]

2. Alat dan Bahan [kembali]

a. Gerbang AND

b. Gerbang OR

c. Inverter ( Gerbang NOT )

Gerbang NOT merupakan gerbang di mana keluarannya akan selalu berlawanan dengan masukannya. Bila pada masukan diberikan tegangan, maka transistor akan jenuh dan keluaran akan bertegangan nol. Sedangkan bila pada masukannya diberi tegangan tertentu, maka transistor akan cut off, sehingga keluaran akan bertegangan tidak nol.

d. Gerbang Exclusive OR (X-OR)

X-OR merupakan gerbang OR yang bersifat exlusif, di mana jika hasil penjumlahan inputnya bernilai ganjil maka outputnya bernilai 1 dan jika hasil penjumlahan inputnya bernilai genap maka outputnya bernilai 0.

e. Logic Probe

Logic Probe akan manampilkan hasil keluaran yang logikanya bernilai 1 atau bernilai 0.

f. Switch SPDT

SPDT adalah singkatan dari Single Pole Double Throw. Sederhananya, terdapat satu terminal umum pada sakelar tempat tegangan dan arus diterapkan dan tegangan serta arus tersebut dapat diarahkan ke terminal yang biasanya terbuka atau biasanya tertutup.

3. Rangkaian Simulasi [kembali]

|

| Rangkaian Percobaan Praktikum Berdasarkan Pada Modul 1 |

|

| Rangkaian Percobaan Praktikum dengan Proteus |

4. Prinsip Kerja [kembali]

Percobaan 2

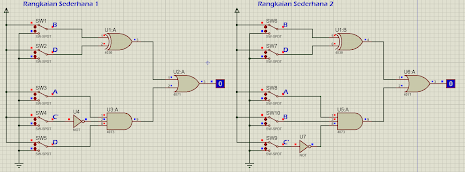

Pada percobaan kali ini terdapat 2 rangkaian sederhana dengan kondisi input rangkaiannya yang berbeda. Komponen yang ada pada rangkaian ini adalah gerbang AND, gerbang NOT, gerbang XOR, gerbang OR, logic probe dan saklar SPDT yang terhubung dengan sumber

Prinsip kerja rangkaian 1

Pada rangkaian terdapat 5 saklar SPDT dimana dua saklar pertama merupakan inputan untuk gerbang logika X-OR dengan kondisi B= 1, D=1 yang nantinya akan menghasilkan keluaran bernilai 0 sesuai dengan prinsip kerja dari gerbang logika X-OR dimana X-OR merupakan gerbang OR yang bersifat exlusif, dimana jika hasil penjumlahan inputnya bernilai ganjil maka outputnya bernilai 1 dan jika hasil penjumlahan inputnya bernilai genap maka outputnya bernilai 0, dan saklar ketiga sampai kelima merupakan inputan untuk gerbang logika AND A=1, C’=1 (pada saklar C' diberikan gerbang logika NOT yang mana menghasilkan keluaran yang berupa kebalikan dari inputannya), D=1 yang akan menghasilkan keluaran bernilai 0 sesuai dengan prinsip kerja gerbang logika AND dimana jika ada salah satu inputnya bernilai 0 maka keluarannya akan bernilai 0 juga. Kemudian keluaran dari gerbang logika X-OR yang bernilai 0 dan gerbang logika AND yang bernilai 0 akan masuk sebagai inputan digerbang logika OR yang menghasilkan keluaran bernilai 0 sesuai dengan prinsip kerja dari gerbang OR yaitu penjumlahan dimana jika semua inputannya bernilai 0 makan otomatis keluarannya akan bernilai 0.

Prinsip kerja rangkaian 2

Pada rangkaian terdapat 5 saklar SPDT dimana dua saklar pertama merupakan inputan untuk gerbang logika X-OR dengan kondisi B= 1, D=1 yang nantinya akan menghasilkan keluaran bernilai 0 sesuai dengan prinsip kerja dari gerbang logika yang bersifat exlusif dimana jika hasil penjumlahan inputnya bernilai ganjil maka outputnya bernilai 1 dan jika hasil penjumlahan inputnya bernilai genap maka outputnya bernilai 0. Kemudian ada gerbang logika AND yang memiliki 3 masukan, masukan dari saklar ketiga bernilai 1, masukan dari saklar keempat bernilai 1 dan masukan dari saklar kelima bernilai 0 yang melewati inverter sehingga yang masukan pada gerbang logika AND bernilai 1 1 0 dan menghasilkan keluaran bernilai 0 sesuai dengan prinsip kerja gerbang logika AND dimana jika ada salah satu inputnya bernilai 0 maka keluarannya akan bernilai 0 juga. Kemudian keluaran dari gerbang logika X-OR yang bernilai 0 dan keluaran dari gerbang logika AND yang bernilai 0 akan menjadi masukan untuk gerbang logika OR yang akan menghasilkan keluaran bernilai 0. Sesuai dengan prinsip kerja dari gerbang OR yaitu jika semua inputannya bernilai 0 maka keluarannya akan bernilai 0.

5. Video Percobaan [kembali]

6. Analisa [kembali]

|

| Data Perhitungan |

|

| Analisa dan Pembahasan |

7. Link Percobaan [kembali]

Komentar

Posting Komentar